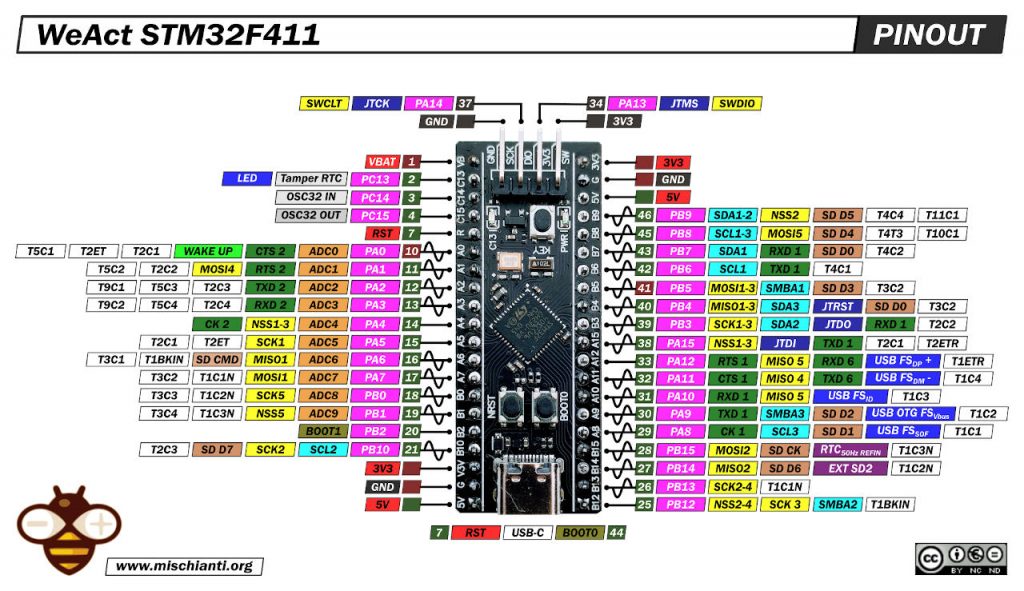

WeAct STM32F411CEU6 Black-Pill: high-resolution pinout and specs

Link to the high resolution pinout image

Here the most used STM32 boards STM32F103C8T6 STM32F401 STM32F411 ST-Link v2 ST-Link v2 official

Description

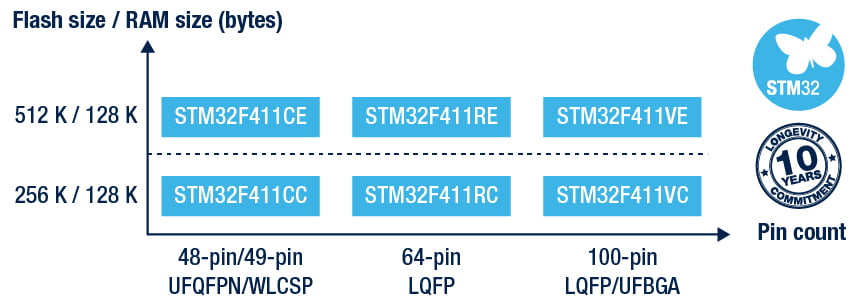

The STM32F411xC/xE devices are based on the high-performance Arm® Cortex® -M4 32-bit RISC core operating at a frequency of up to 100 MHz. The Cortex®-M4 core features a Floating point unit (FPU) single precision which supports all Arm single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security. The STM32F411xC/xE belongs to the STM32 Dynamic Efficiency™ product line (with products combining power efficiency, performance and integration) while adding a new innovative feature called Batch Acquisition Mode (BAM) allowing to save even more power consumption during data batching.

The STM32F411xC/xE incorporate high-speed embedded memories (up to 512 Kbytes of Flash memory, 128 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB bus and a 32-bit multi-AHB bus matrix.

All devices offer one 12-bit ADC, a low-power RTC, six general-purpose 16-bit timers including one PWM timer for motor control, two general-purpose 32-bit timers. They also feature standard and advanced communication interfaces.

The STM32F411xC/xE operate in the – 40 to + 125 °C temperature range from a 1.7 (PDR OFF) to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F411xC/xE microcontrollers suitable for a wide range of applications. (from ST)

Pay attention in the STM32411 series the pins 10 and 41 aren’t 5v tolerant (red square in the pinout diagram)

This board type offers a socket to the bottom to add and External SPI Flash, and SPI1 CS/SCK/MISO/MOSI (PA4/PA5/PA6/PA7) are Routed to footprint for external flash.

Specs

- Dynamic Efficiency Line with BAM (Batch Acquisition Mode)

- 1.7 V to 3.6 V power supply

- – 40°C to 85/105/125 °C temperature range

- Core: Arm® 32-bit Cortex®-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait state execution from Flash memory, frequency up to 100 MHz, memory protection unit, 125 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1), and DSP instructions

- Memories

- Up to 512 Kbytes of Flash memory

- 128 Kbytes of SRAM

- Clock, reset and supply management

- 1.7 V to 3.6 V application supply and I/Os

- POR, PDR, PVD and BOR

- 4-to-26 MHz crystal oscillator

- Internal 16 MHz factory-trimmed RC

- 32 kHz oscillator for RTC with calibration

- Internal 32 kHz RC with calibration

- Power consumption

- Run: 100 μA/MHz (peripheral off)

- Stop (Flash in Stop mode, fast wakeup time): 42 μA Typ @ 25C; 65 μA max @25 °C

- Stop (Flash in Deep power down mode, slow wakeup time): down to 9 μA @ 25 °C; 28 μA max @25 °C

- Standby: 1.8 μA @25 °C / 1.7 V without RTC; 11 μA @85 °C @1.7 V

- VBAT supply for RTC: 1 μA @25 °C

- 1×12-bit, 2.4 MSPS A/D converter: up to 16 channels

- General-purpose DMA: 16-stream DMA controllers with FIFOs and burst support

- Up to 11 timers: up to six 16-bit, two 32-bit timers up to 100 MHz, each with up to four IC/OC/PWM or pulse counter and quadrature (incremental) encoder input, two watchdog timers (independent and window) and a SysTick timer

- Debug mode

- Serial wire debug (SWD) & JTAG interfaces

- Cortex®-M4 Embedded Trace Macrocell™

- Up to 81 I/O ports with interrupt capability

- Up to 78 fast I/Os up to 100 MHz

- Up to 77 5 V-tolerant I/Os

- Up to 13 communication interfaces

- Up to 3 x I2C interfaces (SMBus/PMBus)

- Up to 3 USARTs (2 x 12.5 Mbit/s, 1 x 6.25 Mbit/s), ISO 7816 interface, LIN, IrDA, modem control)

- Up to 5 SPI/I2Ss (up to 50 Mbit/s, SPI or I2S audio protocol), SPI2 and SPI3 with muxed full-duplex I2S to achieve audio class accuracy via internal audio PLL or external clock

- SDIO interface (SD/MMC/eMMC)

- Advanced connectivity: USB 2.0 full-speed device/host/OTG controller with on-chip PHY

- CRC calculation unit

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

How to

- STM32F1 Blue-Pill: pinout, specs, and Arduino IDE configuration (STM32duino and STMicroelectronics)

- STM32: program (STM32F1) via USB with STM32duino bootloader

- STM32: programming (STM32F1 STM32F4) via USB with HID boot-loader

- STM32F4 Black-Pill: pinout, specs, and Arduino IDE configuration

- STM32: ethernet w5500 with plain HTTP and SSL (HTTPS)

- STM32: ethernet enc28j60 with plain HTTP and SSL (HTTPS)

- STM32: WiFiNINA with ESP32 WiFi Co-Processor

- How to use SD card with stm32 and SdFat library

- \STM32: SPI flash memory FAT FS

- STM32: internal RTC, clock, and battery backup (VBAT)

- STM32 LoRa

- STM32 Power saving

- STM32F1 Blue-Pill clock and frequency management

- STM32F4 Black-Pill clock and frequency management

- Intro and Arduino vs STM framework

- Library LowPower, wiring, and Idle (STM Sleep) mode

- Sleep, deep sleep, shutdown, and power consumption

- Wake up from RTC alarm and Serial

- Wake up from the external source

- Backup domain intro and variable preservation across reset

- RTC backup register and SRAM preservation

- STM32 send emails with attachments and SSL (like Gmail): w5500, enc28j60, SD, and SPI Fash

- FTP server on STM32 with w5500, enc28j60, SD Card, and SPI Flash

- Connecting the EByte E70 to STM32 (black/blue pill) devices and a simple sketch example

Datasheet

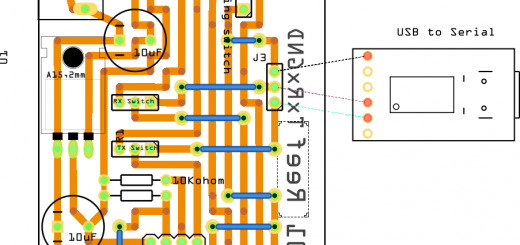

Schema

Thanks

- Arduino

- esp8285

- esp8266

- ESP32

- DOIT ESP32 DEV KIT v1

- ESP32 DevKitC v4

- ESP32 WeMos LOLIN32

- ESP32 WeMos LOLIN32 Lite

- ESP32 WeMos LOLIN D32

- ESP32-wroom-32

- NodeMCU-32S

- ESP32-S

- ESP32-CAM

- ESP32-2432S028 (Cheap Yellow Display)

- ESP32-2432S032 (Cheap Yellow Display)

- ESP32 s2

- ESP32c3

- ESP32s3

- Arduino SAMD

- STM32

- Raspberry Pi